精密电阻在集成电路设计中应用最广泛的电路结构

来源:万利隆电子 阅读量:2000发布时间:2021-04-02

精密电阻在集成电路设计中应用最广泛的电路结构之一,可以说是电流反射镜(CM)。该电路为二端口电路,对输入电流IREF进行处理,根据公式生成输出电流IOUT,其中k为放大(或镜像)系数。描述了一个简单CM的BD配置。显然,使用体积驱动晶体管可以设计更复杂的CM结构。两个MOS器件M1和M2的散装端子连接在一起并连接到输入支路。栅极端子由静态电压Vbias偏置。在输入端,电压降VBS是由输入参考电流流产生的。该电压也通过M2的散端作用于输出支路。因此,采用容积驱动方式,根据式(3)调制输出电流。

精密电阻在集成电路中,MOS晶体管通常由其栅电位控制。然而,流过器件的电流也可以通过大容量源电压VBS进行调制,通常认为这是一种寄生效应,并可能引入不希望的体跨导gmb。在BD设计方法中,输入信号应用于晶体管体,同时偏置电压连接到栅极,以便在源极和漏极之间建立通道。如果保持一个恒定的vg作为偏置电压,并将输入信号施加到体电极上,那么就可以获得类似jfet的晶体管行为。换句话说,反转通道宽度是根据施加到体块上的电压调制的。使用体积作为信号输入可显著降低MOS晶体管克服阈值电压的需要。

精密电阻设计集成电路在阈值电压VTH中嵌入了VBS对漏极电流的影响。MOS晶体管的阈值电压可以用式(3)表示。它也是gm/ID、IC和体驱动设计方法之间非常重要的环节。然而,最后一个缺点可以通过降低电源电压低于PN结的阈值电压或使用昂贵的绝缘体上硅(SOI)制造工艺来有效地缓解。这一步骤将防止寄生的双极型晶体管在基片中的接通。使用体积驱动方法的基本模拟IC构建块的设计范例和电路拓扑。所描述的块已经通过标准CMOS纳米技术和芯片原型的测量评估被硅证明。

此文关键词:

热销电阻

推荐产品

- TO247 1040W高功率电阻-NLR140,,,

- 精密金属膜电阻 PMRYV Series,,,

- 精密高压电阻器 MRI Series,,,

- 超薄铝壳电阻 NUBL,,,

- TO220 20W高功率电阻-NLR30,,,

- TO-220 35W大功率厚膜电阻 NLR-35,,,

- TO220大功率厚膜电阻NLR35,,,

- TO263 50W高功率电阻 (D2PAK)- NLR50 (SM,,,

- TO247 100W高功率电阻-NLR100,,,

- 金属箔电流感测电阻NMS4527,,,

- 合金贴片电阻LFS2512,,,

- 金属箔电流采样电阻LFS1206,,,

- 精密贴片合金电阻LFSS1206,,,

- NMS4320电流检测电阻,,,

- 金属箔电流检测电阻LFS2818,,,

热门资讯

- 全球MICROHM客户隐私权更新通知,,,

- 万利隆将参加日本2018汽车电子技术展,,,

- 2018年电阻打响了涨价的第一枪,那么,,,

- 贴片电阻最重要的五种基本参数,,,

- 万利隆电子将参加2018德国慕尼黑电子,,,

- 万利隆参展日本2018汽车电子技术展,,,

- MICROHM集团出席第十八届韩国·香港商务,,,

- 精密电阻涨价了,为什么2018年电阻市,,,

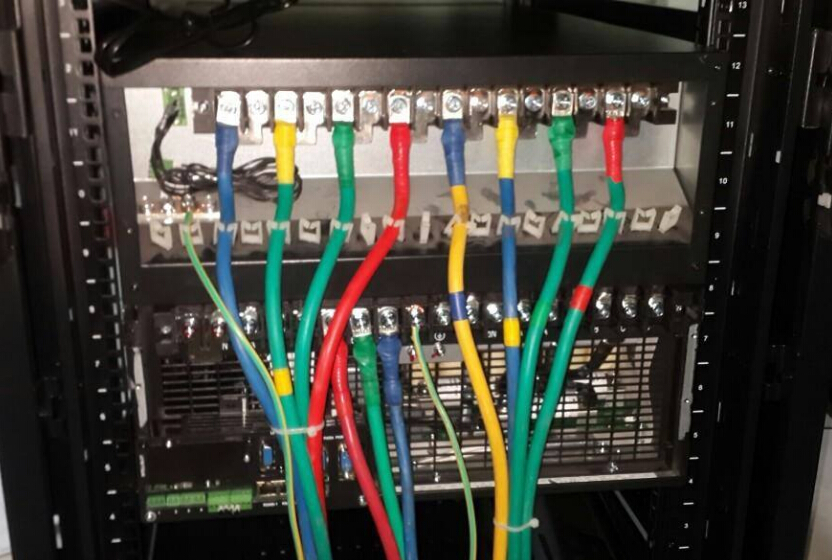

- 精密电阻器在风力发电系统平台的应用,,,

- 0Ω电阻是什么电阻又该如何使用0Ω电阻,,,

- 半导体行业增长趋缓电阻器是否有增长,,,

- 汽车分流电阻shunt应用于新能源汽车电,,,

- 精密采样电阻采样精度影响,精密采样,,,

- 1M至50M电阻值,选精密薄膜电阻还是精密,,,

- 精密电阻助力于可再生能源中太阳能发,,,